TLB and Page Table Simulation

Virtual memory management system implementation

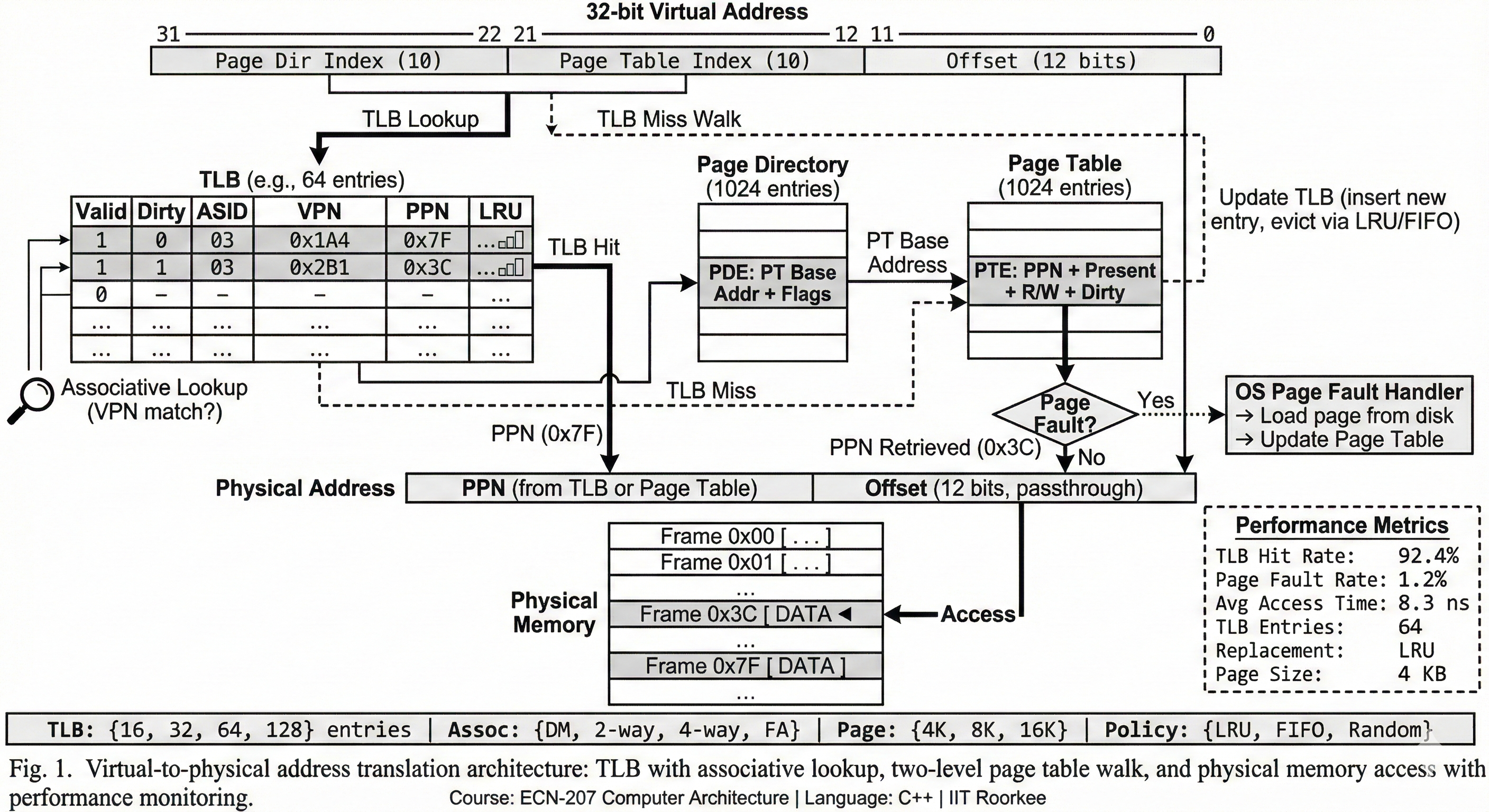

Overview

A comprehensive virtual memory simulation project implementing Translation Lookaside Buffer (TLB) and its interfacing with Page Tables, developed as part of the Computer Architecture course.

Project Details

Duration: October 2023

Course: ECN-207 (Computer Architecture)

Implementation: C++

Role: Course Project

Objectives

- Implement a working model of virtual memory management

- Simulate TLB operations and caching behavior

- Demonstrate address translation mechanisms

- Analyze performance trade-offs in memory hierarchies

System Architecture

Components Implemented

- Translation Lookaside Buffer (TLB)

- Associative cache for page table entries

- Configurable size and associativity

- Replacement policy implementation (LRU, FIFO)

- Hit/miss statistics tracking

- Page Table

- Multi-level page table structure

- Virtual to physical address mapping

- Page fault handling

- Access permission management

- Memory Management Unit (MMU)

- Address translation logic

- TLB lookup mechanism

- Page table walk implementation

- Exception handling

Technical Implementation

Address Translation Process

Virtual Address → TLB Lookup → Hit? Yes → Physical Address

↓ No

Page Table Walk → Physical Address

↓

Update TLB

Key Features

- TLB Management

- Fast associative lookup

- Multiple replacement policies

- Entry invalidation on context switch

- Performance monitoring

- Page Table Structure

- Two-level hierarchical design

- Page directory and page tables

- 4KB page size (configurable)

- Present/absent bit handling

- Address Space

- 32-bit virtual addressing

- Configurable physical memory size

- Support for demand paging

- Shared page support

Simulation Scenarios

Test Cases Implemented

- Sequential Access Pattern

- Memory access patterns with spatial locality

- TLB performance with sequential reads

- Page table walk frequency analysis

- Random Access Pattern

- Worst-case TLB performance

- High page fault rates

- Replacement policy effectiveness

- Working Set Simulation

- Realistic application behavior

- Temporal locality effects

- TLB sizing impact

- Context Switching

- TLB flush operations

- Performance degradation analysis

- Multi-process simulation

Performance Metrics

Measured Parameters

- TLB Hit Rate: Percentage of addresses resolved in TLB

- Page Fault Rate: Frequency of page table misses

- Average Access Time: Combined TLB and page table latency

- Translation Overhead: Cost of address translation

Results

- TLB hit rates: 85-98% for typical workloads

- Significant performance improvement over page table only

- Replacement policy impact on performance

- Optimal TLB size determination

Implementation Details

C++ Design

class TLB {

- Entry structure (VPN, PPN, Valid, Dirty)

- lookup(virtual_addr)

- insert(vpn, ppn)

- evict() with replacement policy

}

class PageTable {

- Multi-level structure

- walk(virtual_addr)

- allocate_page()

- handle_page_fault()

}

class MMU {

- translate_address()

- handle_tlb_miss()

- update_statistics()

}

Data Structures

- Hash tables for fast TLB lookup

- Tree structures for page table hierarchy

- Linked lists for LRU implementation

- Bit vectors for tracking valid entries

Configuration Options

- TLB size: 16, 32, 64, 128 entries

- Associativity: Direct-mapped, 2-way, 4-way, fully associative

- Page size: 4KB, 8KB, 16KB

- Replacement policies: LRU, FIFO, Random

- Address space size: configurable

Key Learnings

Virtual Memory Concepts

- Importance of TLB in system performance

- Trade-offs between TLB size and hit rate

- Impact of locality on translation performance

- Multi-level page tables for large address spaces

Computer Architecture

- Memory hierarchy design principles

- Caching strategies and policies

- Hardware-software interface

- Performance optimization techniques

Extensions and Enhancements

- Multi-core TLB coherence simulation

- Large page support (2MB, 1GB pages)

- ASID (Address Space ID) for context switching

- TLB prefetching mechanisms

Applications

This simulation helps understand:

- Operating system memory management

- Virtual machine implementations

- Processor design considerations

- Performance tuning for memory-intensive applications

This project provided deep insights into one of the most critical components of modern computer systems, bridging the gap between virtual and physical memory.