CNN on FPGA for MNIST Digit Classification

Hardware implementation of neural networks on FPGA

Overview

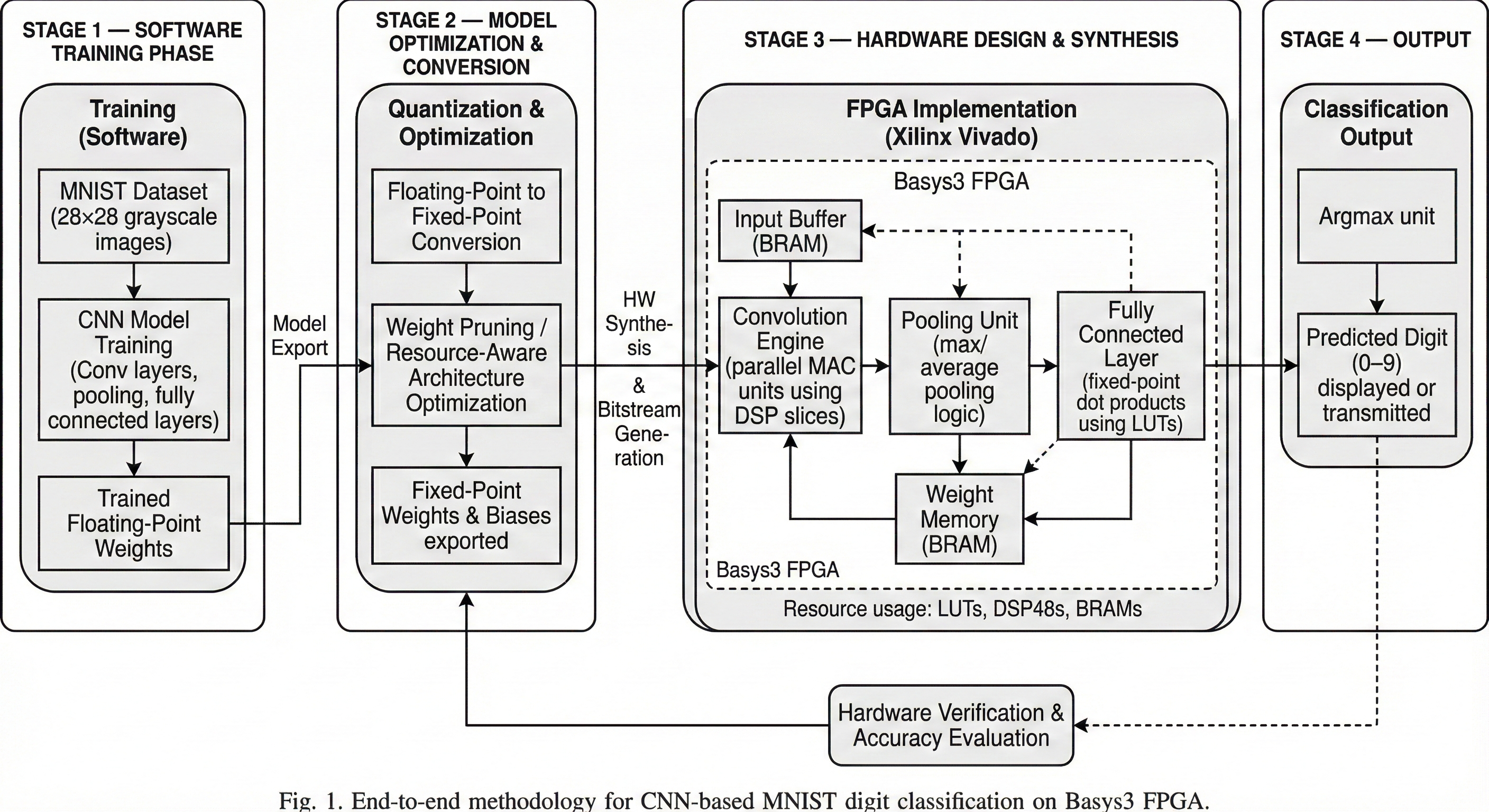

This project implements a Convolutional Neural Network (CNN) on FPGA hardware for real-time MNIST digit classification, demonstrating the intersection of deep learning and hardware acceleration.

Project Details

Duration: August 2025 – September 2025

Platform: Basys3 FPGA Board

Tools: Xilinx Vivado

Technical Implementation

Architecture

- Custom CNN architecture optimized for FPGA resources

- Hardware-level implementation of convolution operations

- Real-time inference capabilities

- Resource-efficient design for embedded deployment

Hardware Specifications

- FPGA Board: Basys3

- Development Tool: Xilinx Vivado

- Target Dataset: MNIST handwritten digits

- Performance: Real-time classification

Key Features

- Hardware Acceleration: Leveraged FPGA parallelism for fast inference

- Resource Optimization: Efficient use of FPGA resources (LUTs, DSPs, BRAMs)

- Real-time Processing: Low-latency digit recognition

- Verified Implementation: Tested and verified on actual hardware

Technical Challenges

- Resource Constraints: Optimizing network architecture to fit FPGA limitations

- Fixed-point Arithmetic: Converting floating-point operations to fixed-point

- Memory Management: Efficient use of on-chip memory for weights and activations

- Timing Closure: Meeting timing requirements for reliable operation

Results

- Successfully classified MNIST digits in real-time

- Verified functionality on Basys3 FPGA board

- Demonstrated feasibility of CNN deployment on resource-constrained hardware

Skills Developed

- FPGA design and implementation

- Hardware-software co-design

- Digital signal processing

- Verilog/VHDL programming

- Neural network optimization for embedded systems